# ENGR4300 Fall 2005 Test 3S

| <b>Name</b>   | <u>solution</u> |   |

|---------------|-----------------|---|

| Section       |                 |   |

|               |                 |   |

| Ouestion 1 (  | 25 points)      |   |

|               | _               | _ |

| Question 2 (2 | 25 points)      |   |

| Question 3 (  | 25 points)      |   |

| Question 4 (  | 25 points)      |   |

|               |                 |   |

| Total (100 p  | oints):         |   |

Please do not write on the crib sheets.

On all questions: SHOW ALL WORK. BEGIN WITH FORMULAS, THEN SUBSTITUTE VALUES <u>AND UNITS</u>. No credit will be given for numbers that appear without justification.

## **Question 1 – Astable Multivibrator (25 points)**

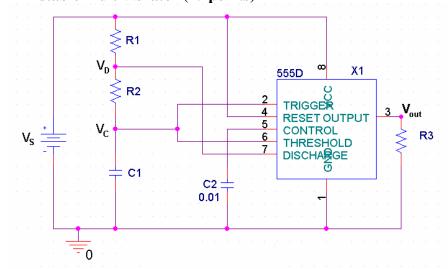

The multivibrator above was built with the 555 timer chip shown. In the diagram, Vs is the source voltage, Vc is the voltage across the capacitor C1, and  $V_D$  is the voltage at the discharge pin of the timer. You are given the following component values:

Test A: R1 = 4.7k ohms R2 = 6.8k ohms C1 =  $0.68\mu F$  Vs = 6V Test B: R1 = 2.2k ohms R2 = 4.7k ohms C1 =  $1.5\mu F$  Vs = 12V

Test C: R1 = 6.8k ohms R2 = 8.6k ohms  $C1 = 0.47\mu F$  Vs = 5V

1) Calculate the on time and off time of the multivibrator. (4 pt)

$$T1 = 0.693(R1 + R2)C1$$

$T1 = 0.693(4.7K + 6.8K)(0.68\mu) = 5.42ms$   $T2 = 0.693(R2)C1$   $T2 = 0.693(6.8k)(0.68\mu) = 3.20ms$

Test A: Ton = 5.42ms Toff = 3.20ms Test B: Ton = 7.17ms Toff = 4.89ms Test C: Ton = 5.02ms Toff = 2.80ms

2) Calculate the frequency and period of the multivibrator. (4 pt)

$$T=Ton + Toff \quad f=1/T \qquad T=5.42m+3.20m = 8.62ms \quad f=1/8.62m=116Hz$$

Test A: T = 8.62ms f = 116 HzTest B: T = 12.06ms f = 82.9 HzTest C: T = 7.82ms f = 128 Hz

3) Calculate the duty cycle of the multivibrator. (2 pt)

$$DC = 100*Ton/T$$

$DC=100*5.42m/8.62m=62.9\%$

Test A: DC = 62.9% Test B: DC = 59.5%

Test C: DC = 64.2%

4) In theory, what are the maximum and minimum voltage across the capacitor, Vc? (2 pt)

$$Vmin = Vs/3$$

$Vmax = 2*Vs/3$   $Vmin=6/3=2V$   $Vmax = 2*6/3 = 4V$

Test A: Vmin = 2V Vmax = 4V

Test B:  $Vmin = 4V \quad Vmax = 8V$

Test C:  $Vmin = 1.67V \ Vmax = 3.33V$

5) When the transistor inside the 555 timer is closed, the output at pin 7 is grounded, and therefore, equal to zero. When the transistor is open, the output at pin 7 can be found using the voltage divider formed by R1 and R2. Find an expression for the voltage at pin 7 (when pin 7 is not grounded) in terms of the voltage across the capacitor, Vc, the source voltage, Vs, and the two resistors R1 and R2. [Hint: Recall how you calculate the voltage at the non-inverting input for a Schmitt trigger.] Do not substitute values. (3 pt)

$$V_D = \left(\frac{R2}{R1 + R2}\right) (V_S - V_C) + V_C$$

This can be simplified further, but it is not necessary.

6) Use the equation in 5) to find the maximum and minimum voltage at pin 7 when the transistor is open. (2 pt)

$$V_{Dlow} = [6.8k/(6.8k+4.7k)](6-2) + 2 = 4.36V$$

$V_{Dhigh} = [6.8k/(6.8k+4.7k)](6-4) + 4 = 5.18V$

Test A:

$$V_{Dlow} = 4.36V$$

$V_{Dhigh} = 5.18V$

Test B:

$$V_{Dlow} = 9.44V$$

$V_{Dhigh} = 10.72V$

Test C:

$$V_{Dlow} = 3.53V$$

$V_{Dhigh} = 4.27V$

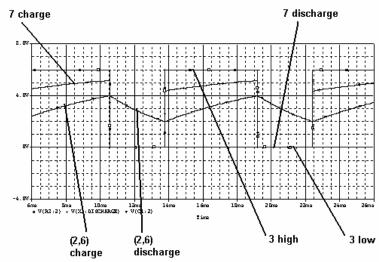

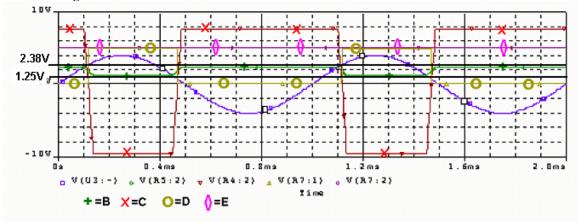

7) On the graph below, identify the outputs at pin (2, 6), 7 and 3 of the multivibrator. Identify both parts of the cycle for each. (6 pt)

This shows the basic shape of the signals. The image on each test was different.

# **Question 2 – Combinational Logic Circuits (25 points)**

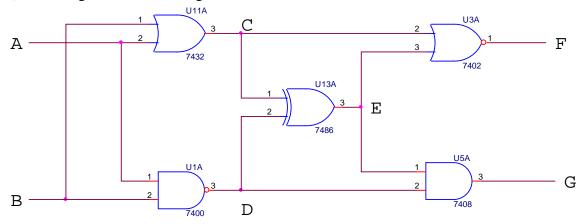

Test A and B:

1) You are given the following circuit

a) Fill out the truth table below (10 pt)

| A | В | C | D | Е | F | G |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 |

b) What gate is the output at G equivalent to (circle one)? (1 pt)

AND NAND OR NOR XOR XNOR NOT

2) Fill out the truth table below to prove the following relationship: (14 pt)

if

$$Q = (\overline{A} \bullet B) + (A \bullet \overline{B}) + (A \bullet B)$$

then  $Q = A + B$

| A | В | $\overline{A}$ | $\overline{B}$ | $\overline{A} \bullet B$ | $A \bullet \overline{B}$ | $A \bullet B$ | Q | A+B |

|---|---|----------------|----------------|--------------------------|--------------------------|---------------|---|-----|

| 0 | 0 | 1              | 1              | 0                        | 0                        | 0             | 0 | 0   |

| 0 | 1 | 1              | 0              | 1                        | 0                        | 0             | 1 | 1   |

| 1 | 0 | 0              | 1              | 0                        | 1                        | 0             | 1 | 1   |

| 1 | 1 | 0              | 0              | 0                        | 0                        | 1             | 1 | 1   |

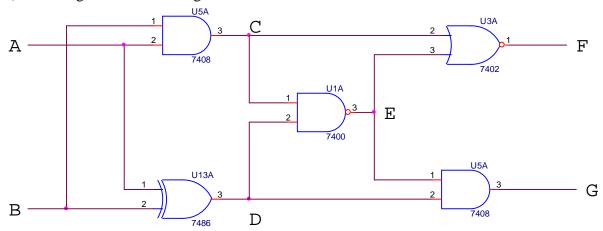

Test C:

1) You are given the following circuit

**Fall 2005**

a) Fill out the truth table below (10 pt)

| A | В | C | D | Е | F | G |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 | 0 |

b) What gate is the output at G equivalent to (circle one)? (1 pt)

AND NAND OR NOR XOR XNOR NOT

2) Fill out the truth table below to prove the following relationship: (14 pt)

if

$$Q = (\overline{A} + B) \bullet (A + \overline{B}) \bullet (A + B)$$

then  $Q = A \bullet B$

| A | В | $\overline{A}$ | $\overline{B}$ | $\overline{A} + B$ | $A + \overline{B}$ | A + B | Q | $A \bullet B$ |

|---|---|----------------|----------------|--------------------|--------------------|-------|---|---------------|

| 0 | 0 | 1              | 1              | 1                  | 1                  | 0     | 0 | 0             |

| 0 | 1 | 1              | 0              | 1                  | 0                  | 1     | 0 | 0             |

| 1 | 0 | 0              | 1              | 0                  | 1                  | 1     | 0 | 0             |

| 1 | 1 | 0              | 0              | 1                  | 1                  | 1     | 1 | 1             |

#### **Question 3 – Sequential Logic Gates (25 points)**

#### Quiz A and B:

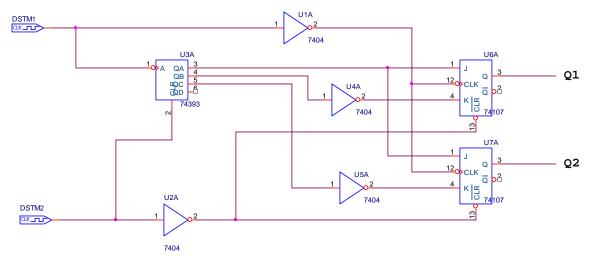

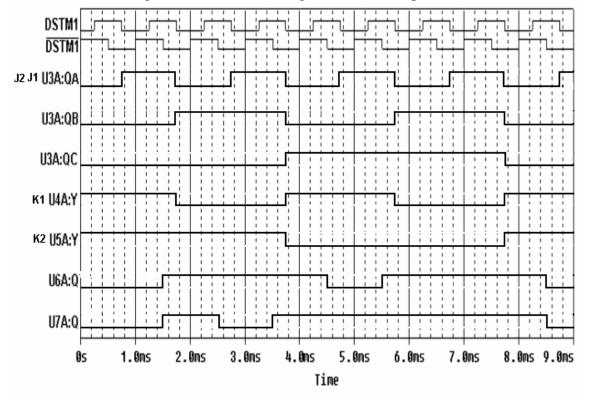

You are given the following circuit DSTM1 provides the clock for the counter. *DSTM*1 provides the clock to the two flip flops. DSTM2 provides an initial reset pulse to all the sequential chips. Therefore, you can assume that QA, QB, QC, QD, Q1, and Q2 are all initially low.

1) Sketch the timing trace for each of the signals shown. (14 pt)

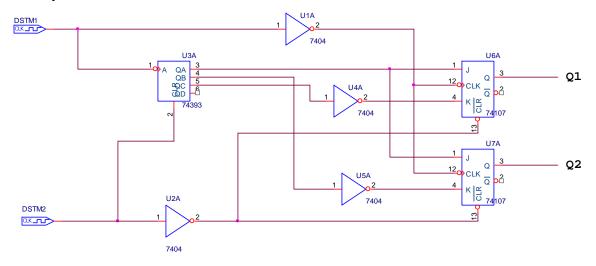

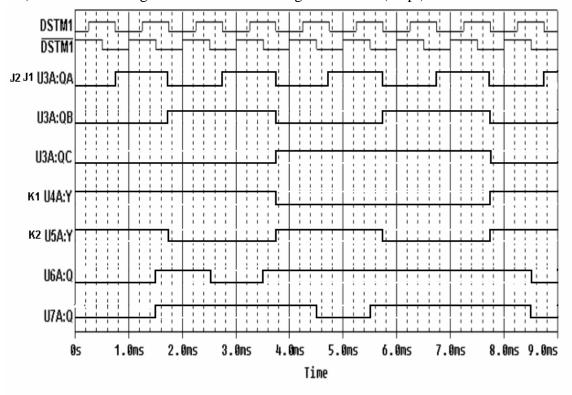

### Quiz C:

You are given the following circuit DSTM1 provides the clock for the counter. *DSTM*1 provides the clock to the two flip flops. DSTM2 provides an initial reset pulse to all the sequential chips. Therefore, you can assume that QA, QB, QC, QD, Q1, and Q2 are all initially low.

1) Sketch the timing trace for each of the signals shown. (14 pt)

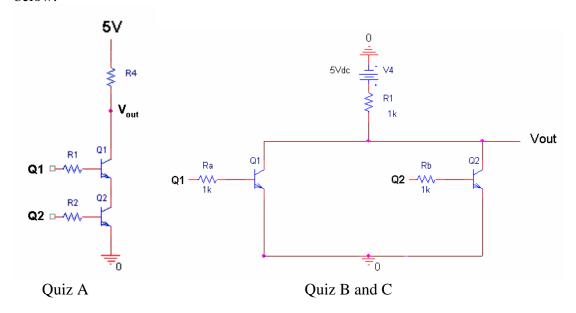

2) We take the output of this circuit and use it as the input to the transistor circuit shown below:

Fill in the following table for all possible values of Q1 and Q2. (4 pt)

| I ill ill the following table for all pos |                      |

|-------------------------------------------|----------------------|

| Quiz A                                    | Quiz B and C         |

|                                           |                      |

| Q1 Q2 Vout                                | Q1 Q2 Vout           |

| 0V 0V 5V                                  | 0V 0V 5V             |

| 0V 5V 5V                                  | $0V \mid 5V \mid 0V$ |

| 5V 0V 5V                                  | $5V \mid 0V \mid 0V$ |

| 5V 5V 0V                                  | 5V 5V 0V             |

|                                           |                      |

|                                           |                      |

3) What are the values of the signals at Q1, Q2 and Vout after 8.9 milliseconds? (3 pt)

All Tests:

Q1: 0V

Q2: 0V

Vout: 5V

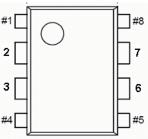

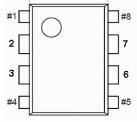

Ouiz A and B

4) IC chips have a standard numbering convention that you should now know. Label pins #1-8 on the IC below. (HINT: It doesn't matter what the chip's function is – just label #1, #2, ...). (1 pt)

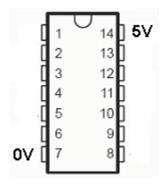

5) Like op-amps, IC chips need two power connections in order to function. Label the power (Vcc) and ground pins on the 7404 IC chip pictured below with the appropriate *voltage values*. (1 pt)

6) The 7404 chip contains more than one inverter. How many does it contain? (1 pt)

6

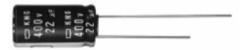

7) You've primarily used two types of capacitors in the studio: electrolytic and ceramic disc, each shown below:

Electrolytic:

Ceramic Disc:

Which one is polarized (e.g. has a + and - lead) (circle one)? (1 pt)

neither

electrolytic

ceramic disc

both

Quiz C

4) IC chips have a standard numbering convention that you should now know. Label pins #1-8 on the IC below. (HINT: It doesn't matter what the chip's function is – just label #1, #2, ...). (1 pt)

- 5) We've talked about the use of bypass capacitors when working with digital logic chips. Which answer below best describes where they should be located and why we use them? (1 pt)

- a. Place one or more between digital logic inputs and ground to smooth the sharp transients of digital switching signals that could otherwise corrupt proper chip operation.

- b. Place one or more in series with logic power (Vcc) where it enters the protoboard to filter noise coming from the power supply.

- c. Place one or more in parallel with Vcc and ground at each chip to filter noise.

- d. Place only one between Vcc and high speed logic chip outputs to suppress output oscillation (e.g. ringing).

- 6) What was the recommended range of bypass capacitor values given for the TTL logic family used in the studio? (circle one) (1 pt)

a) 0.1pF - 0.5pF

b) 0.01nF - 0.1nF

c) 0.01uF - 0.1uF

d) 0.1uF - 10uF

e) 10uF - 100uF

f) I don't know because I slept through that lecture.

7) You've primarily used two types of capacitors in the studio: electrolytic and ceramic disc, each shown below:

Electrolytic:

Ceramic Disc:

Which one is polarized (e.g. has a + and - lead) (circle one)? (1 pt)

neither

electrolytic

ceramic disc

both

#### **Question 4 – Switching Circuits (25 points)**

- 1) In the circuit shown, circle the model of a Schmitt trigger. (1 pt)

- 2) What is the reference voltage of the Schmitt trigger model? (1 pt)

Test A:

$$Vref = 2V$$

Test B:  $Vref = 3V$  Test C:  $Vref = 2V$

3) If the op-amp is putting out its maximum voltage at C, what is the voltage at point B, the non-inverting input to the op-amp? (3 pt)

$$v + = \left(\frac{R_2}{R_1 + R_2}\right) (v_{out} - V_{ref}) + V_{ref} \quad v + = [2k/(2k + 30k)](8-2) + 2 = 2.375V$$

Test A:

$$v + = 2.38V$$

Test B:  $v + = 3.33V$  Test C:  $v + = 2.33V$

4) If the op-amp is putting out is minimum voltage at point C, what is the voltage at point B, the non-inverting input to the op-amp? (3 pt)

$$v + = \left(\frac{R_2}{R_1 + R_2}\right) (v_{out} - V_{ref}) + V_{ref} \quad v_{v+1} = [2k/(2k+30k)](-10-2) + 2 = 1.25V$$

Test A:

$$v + = 1.25V$$

Test B:  $v + = 2.48V$  Test C:  $v + = 1.57V$

- 5) On the following plot, the input at point A is shown.

- a) Mark the upper and lower thresholds of the hysteresis (2 pt), and

- b) sketch and label the output at points B, C, D and E for the input shown. (12 pt)

Many of the signals will overlap. Use the PSpice labeling convention to identify the signals by drawing unique symbols on *important parts* of each trace. Note that the input

has a little box. Use the following:  $B = + C = \times D = O$  and  $E = \lozenge$ .

This plot shows the basic shape of the signals for all three tests. Specific high and low values are given below.

- Test A: Signals change when input rises above 2.38V or falls below 1.25V Signal B toggles between 1.25 and 2.38 volts. (H-L-H-L-H) Signal C toggles between +8V and -10V (H-L-H-L-H)

- Test B: Signals change when input rises above 3.33V or falls below 2.48V Signal B toggles between 2.48 and 3.33 volts. (H-L-H-L-H) Signal C toggles between +10V and -8V (H-L-H-L-H)

- Test C: Signals change when input rises above 2.33V or falls below 1.57V Signal B toggles between 1.57 and 2.33 volts. (H-L-H-L-H) Signal C toggles between +9V and -7V (H-L-H-L-H)

- All Tests: Signal D toggles between 0V and some voltage less than 5V (L-H-L-H-L) (You do not know enough about diodes to know the exact voltage, so we accepted anything in this range that was recognizable as not zero.) Signal E is constant at 5V

8) Are the LEDs on or off at the following times (3 points)?

| time  | LED1 | LED2 |

|-------|------|------|

| 0.3ms | ON   | ON   |

| 0.8ms | OFF  | ON   |

| 1.2ms | ON   | ON   |