#### Quiz 4

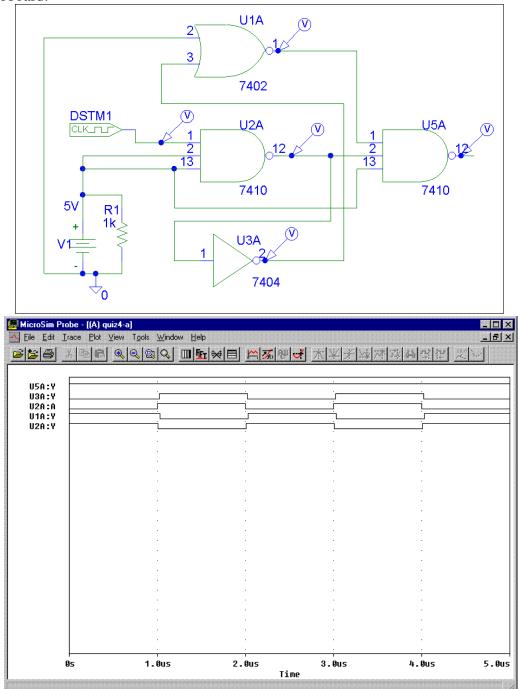

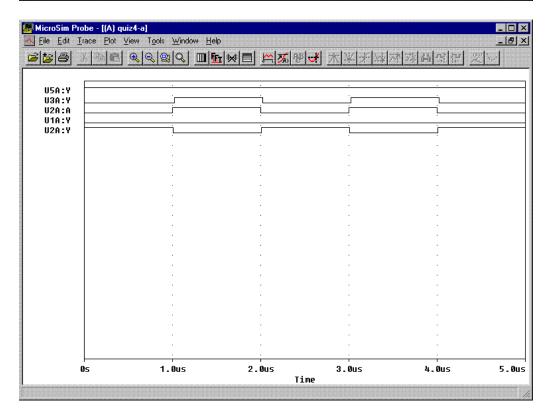

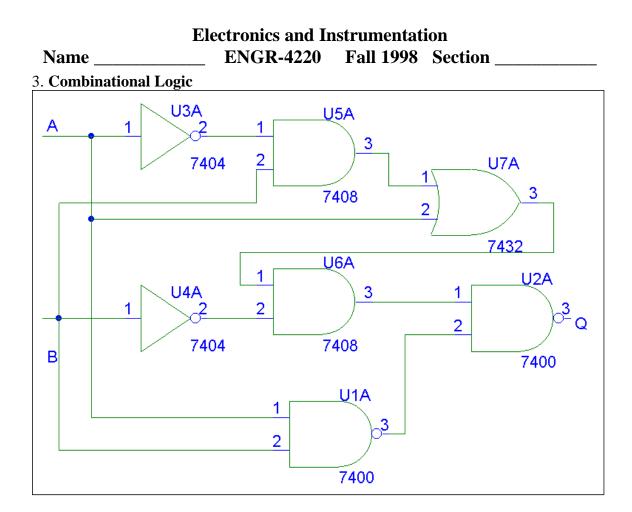

1. **Logic Gates** You should recognize the logic gates in the figure below as those used in the first part of Experiment 11. If you performed the same kind of experiment as you did when you tested the gates on the protoboard, which of the following three figures is correct for the inputs shown? The digital clock represents the function generator and the other inputs are DC values obtained by connecting to the ground and  $V_{CC}$  rails on the protoboard.

# **Electronics and Instrumentation** Name \_\_\_\_\_ ENGR-4220 Fall 1998 Section \_\_\_\_\_

| USA:Y U2A:A U1A:Y U2A:Y U2A:Y | U3A:Y |        | 0s | 1.0us  | 2.0us                                         | 3.0us  | 4.Ous | 5.0 |

|-------------------------------|-------|--------|----|--------|-----------------------------------------------|--------|-------|-----|

| U3A:Y                         | U5A:Y |        |    |        |                                               |        | •     |     |

| U3A:Y                         | U5A:Y |        |    |        |                                               |        |       |     |

| U3A:Y                         | U5A:Y |        |    |        |                                               |        |       |     |

| U3A:Y                         | U5A:Y |        |    |        |                                               |        | •     |     |

| U3A:Y                         | U5A:Y |        |    |        |                                               | •      |       |     |

| U3A:Y                         | USA:Y |        |    | •      | •                                             | •      | •     |     |

| U3A:Y                         | U5A:Y |        |    |        |                                               |        | •     |     |

| U3A:Y                         | USA:Y |        |    |        |                                               | •      |       |     |

| U3A:Y                         | USA:Y |        |    | •      | •                                             | •      | •     |     |

| U3A:Y                         | U5A:Y |        |    |        |                                               |        |       |     |

| U3A:Y                         | U5A:Y |        |    |        | •                                             |        |       |     |

| U3A:Y                         | U5A:Y | U2A:Y  |    |        |                                               |        | !     |     |

|                               | USA:Y | U1A:Y  |    | !<br>i | ۲ <u>ــــــــــــــــــــــــــــــــــــ</u> | !<br>i |       |     |

| IIS0-V                        |       | U3A:Y  |    | ;<br>; | i                                             | ;      | i     |     |

|                               |       | 1150.0 |    |        |                                               |        |       |     |

# Electronics and Instrumentation Name \_\_\_\_\_\_\_ ENGR-4220 Fall 1998 Section \_\_

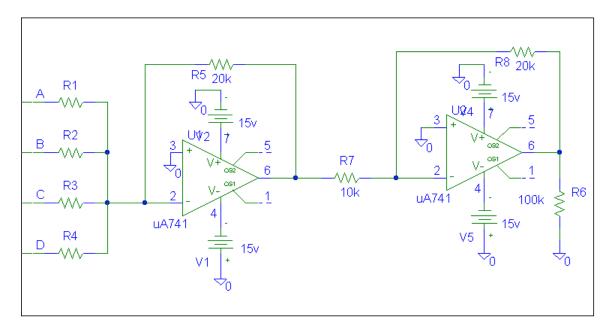

# 2. Digital-to-Analog Converter

The configuration of op-amps and resistors shown below can produce an analog output voltage (across the last 100k resistor on the right) equal to the binary word ABCD input at the left. Assume that you are working with TTL devices, so the voltage levels for ones and zeros are TTL levels (0V and 5V). Select values for R1, R2, R3, and R4 so that the output voltage will be the decimal equivalent of ABCD.

R1 = R2 = R3 = R4 =

Show that your values work for the two binary numbers ABCD = 1110 and ABCD = 1001. Be careful, this is not exactly the same configuration seen on last spring's quiz.

Which of the following truth tables is correct for this circuit?

| А      | В      | Q      |

|--------|--------|--------|

| 0      | 0      | 1      |

| 0      | 1      | 0      |

| 1      | 0      | 1      |

| 1      | 1      | 0      |

| -      | -      | ÷      |

| А      | В      | 0      |

| A<br>0 | 0      | Q<br>0 |

| 0      |        | 1      |

| 1      | 1<br>0 | 1<br>0 |

| 1      | 1      | 1      |

| 1      | 1      | 1      |

| •      | п      | 0      |

| A      | В      | Q<br>1 |

| 0      | 0      | 1      |

| 0      | 1      | 1      |

| 1      | 0      | 0      |

| 1      | 1      | 1      |

|        |        |        |

| A<br>0 | В      | Q<br>1 |

| 0      | 0      | 1      |

| 0      | 1<br>0 | 0      |

| 1      | 0      | 1      |

|        | 0      | 1      |

## Electronics and Instrumentation ENGR-4220 Fall 1998 Section

## Name \_\_\_\_\_

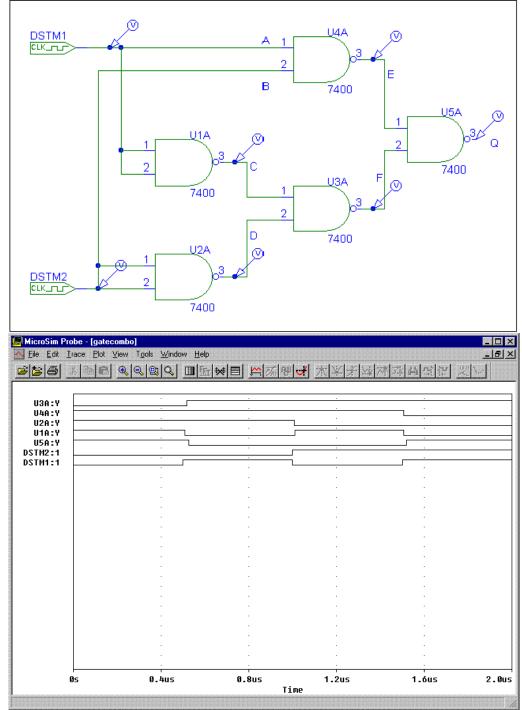

#### 4. NAND Gate Circuits

It is possible to configure all standard gates using just NAND gates. The figure below shows one such combination of NANDs. There are seven voltages displayed on the transient voltage plot below. Identify which signal goes with which location. See if you can identify what the overall circuit is equivalent to. (You might want to construct the truth table for this purpose.) Remember that each standard gate comes in two forms, one that performs a particular logical function and one that performs the complement of (or NOT the) function.

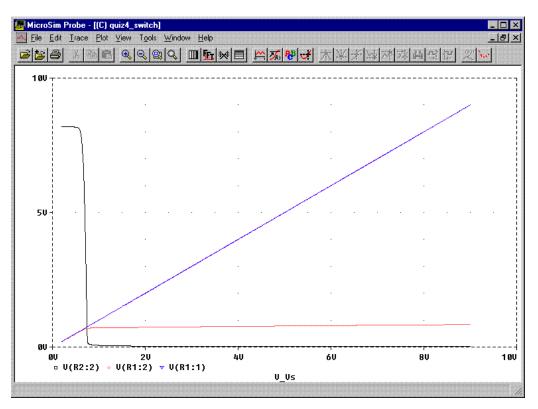

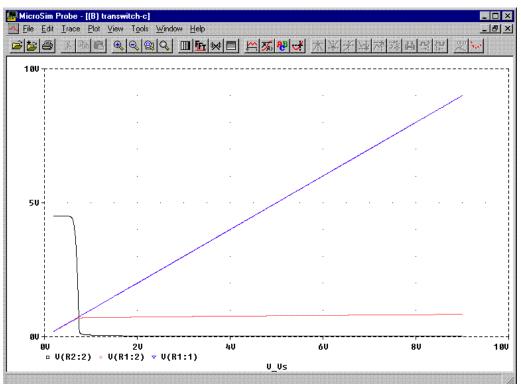

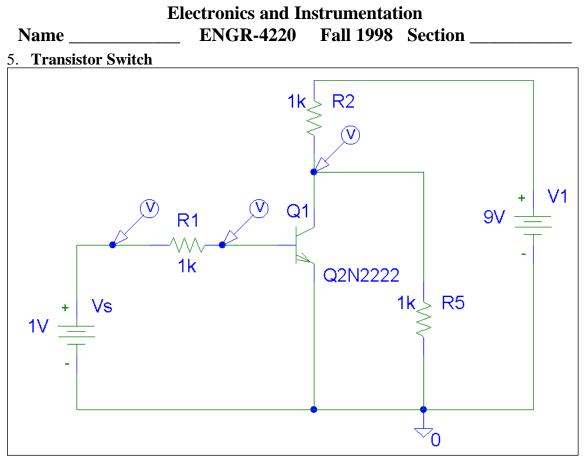

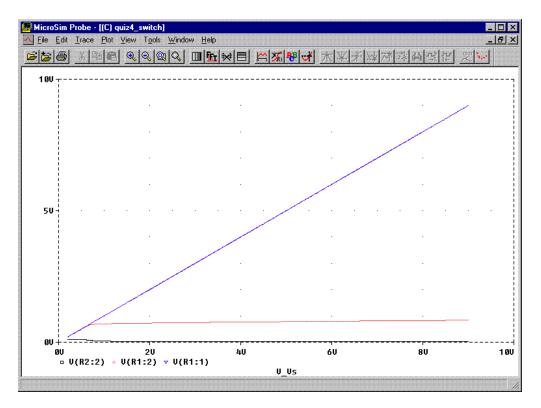

In the circuit above, the voltage source Vs is ramped up from zero to 9 volts and the voltages at the source and two other points are monitored. Which of the following plots goes with this circuit?

#### Name