#### Sample Question: Flip Flops and Counters

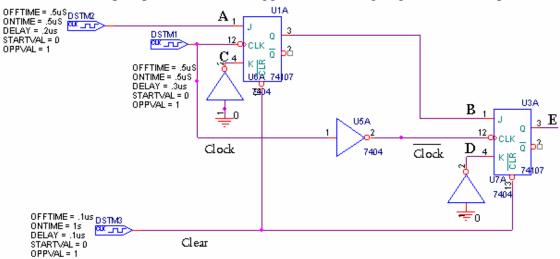

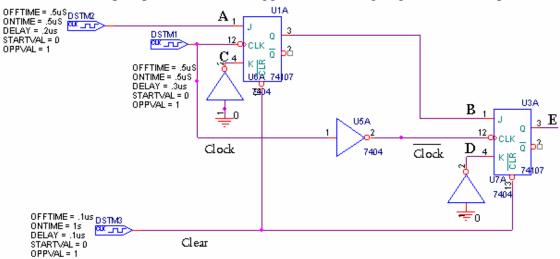

The following is a diagram of a circuit from PSpice. The "Clear" signal initializes the flip flop. Therefore, once it goes high, the flip flop outputs Q=0 and  $\overline{Q}$  =1. The clock for the first flip flop is DSTM1 and the clock for the second flip flop is DSTM1 *inverted*. Remember that flip flops and counters trigger on the falling edge of the clock pulse.

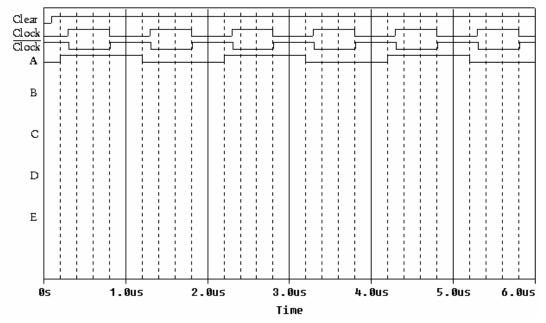

a) The following figure shows the clear signal, the clocks and the input at A. Draw the traces at B, C, D and E.

b) If the clock for a counter (74393) was attached to signal A, what would the output look like after 3.0us. (Assume the counter has also been cleared, therefore QA=0V, QB=0V, QC=0V, QD=0V at time 0s). Express your answer in volts.

$$QA = QB = QC = QD =$$

#### Sample Question: Flip Flops and Counters \*\*\* ANSWER \*\*\*

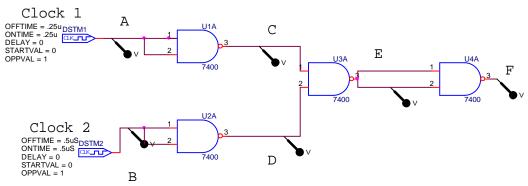

The following is a diagram of a circuit from PSpice. The "Clear" signal initializes the flip flop. Therefore, once it goes high, the flip flop outputs Q=0 and  $\overline{Q}$  =1. The clock for the first flip flop is DSTM1 and the clock for the second flip flop is DSTM1 *inverted*. Remember that flip flops and counters trigger on the falling edge of the clock pulse.

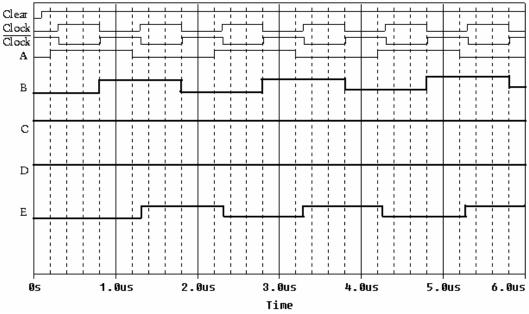

a) The following figure shows the clear signal, the clocks and the input at A. Draw the traces at B, C, D and E.

[Some explanation: C and D are inverted from ground. This means they are always high. Note that the flip flops only change on the falling edges of the clock. The first flip flop will look at J and K when Clock goes down at 0.8 us. Since at that time A(=J) is high and C(=K) is high, the flip flop toggles and B goes high. The next time that Clock goes high to low at 1.8us, A is low and C is still high. This time, the flip flop should be equal to J(A) and B goes low again. This sequence continues for B. The signal at E changes on the falling edge of Clockbar(the inverted clock signal). Its inputs are J=B and K=5V. At 0.3us, B is low, so E stays low. At 1.3us, B is high, so E toggles to high. At 2.3us, B is low, so E goes low again. The sequence continues.]

b) If the clock for a counter (74393) was attached to signal B, what would the output look like after 6.0us. (Assume the counter has also been cleared, therefore QA=0V, QB=0V, QC=0V, QD=0V at time 0s). Express your answer in volts.

QA = 5V QB = 5V QC = 0V QD = 0V

[Some explanation: The counter "counts" on the falling edge of the clock. Since B has three pulses since 0s, the counter should count up to three. In binary, that is 0011. Note that QA is the lowest order bit.]

#### Sample Question: Boolean Algebra

It is possible to configure all standard gates using just NAND gates. The figure below show one such combination of NANDS.

a. Identify which trace belongs to which point in the circuit.

b. Write a boolean expression for this circuit (Do not simplify).

| a Dramartian of             | h Dulas of Combination                                                                      | a DaManaan'a Laura                                        |

|-----------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| a. Properties of            | b. Rules of Combination                                                                     | c. DeMorgan's Laws                                        |

| Operations                  |                                                                                             |                                                           |

| (a1) A ? $0 = 0$            | (b1) A ? B = B ? A                                                                          | $(c1) \sim (A?B) = \sim A + \sim B$                       |

| (a2) $A + 0 = A$            | (b2) A + B = B + A                                                                          | $(c2) \sim (A + B) = \sim A ? \sim B$                     |

| (a3) A ? $1 = A$            | (b3) A ? (B+C) = (A?B) + (A?C)                                                              |                                                           |

| (a4) $A + 1 = 1$            | (b4) A ? (B?C) = (A?B) ? C                                                                  | d. Other Rules                                            |

| (a5) A? A = A               | (b5) $A + (B+C) = (A+B) + C$                                                                | (d1)A : B = ~A?B + A?~B                                   |

| (a6) A + A = A              | (b6) A + (A?B) = A                                                                          | $(d1)A \operatorname{xor} B = \sim AandB +$               |

|                             |                                                                                             | Aand~B                                                    |

| (a7) A? $\sim$ A = 0        | (b7) A? $(A+B) = A$                                                                         | $(d2) \sim (A!  B) = \sim A? \sim B + A?B$                |

| (a8) $A + \sim A = 1$       | (b8) A? $(\sim A + B) = A? B$                                                               | $(d2) \sim (A \operatorname{xor} B) = \sim Aand \sim B +$ |

|                             |                                                                                             | AandB                                                     |

| (a9) $\sim$ ( $\sim$ A) = A | $(b9) A + (\sim A ? B) = A + B$                                                             |                                                           |

|                             | $(b10) \sim A + (A?B) = \sim A + B$                                                         |                                                           |

|                             | $(b11) \sim \mathbf{A} + (\mathbf{A}? \sim \mathbf{B}) = \sim \mathbf{A} + \sim \mathbf{B}$ |                                                           |

Note that the NOT operation is indicated here by ~ instead of as a bar over the letter. You are free to use either notation. You can indicate the rule by the letter. [Note to students: Unfortunately, the PDF writer has trouble with the symbol font. In the above chart, the ? in sections a, b and c are AND symbols and the meaning of the ? in section d can be found in the restatement of the rule.]

c. Using the Boolean Algebra rules shown above, prove that this combination of gates works as a NOR gate.

## Sample Question: Boolean Algebra \*\* ANSWER \*\*

It is possible to configure all standard gates using just NAND gates. The figure below show one such combination of NANDS.

a. Identify which trace belongs to which point in the circuit.

$A = Clock1; B = Clock2; C = \neg A = X; D = \neg B = Y; E = \neg (XandY) = Z; F = \neg E = W$

b) Write a boolean expression for this circuit (Do not simplify).

$F = \sim [\sim (\ \sim A \ and \ \sim B \ )]$

| a. Properties of            | b. Rules of Combination                                                            | c. DeMorgan's Laws                                        |

|-----------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Operations                  |                                                                                    |                                                           |

| (a1) A ? $0 = 0$            | (b1) A ? B = B ? A                                                                 | $(c1) \sim (A?B) = \sim A + \sim B$                       |

| (a2) $A + 0 = A$            | (b2) A + B = B + A                                                                 | $(c2) \sim (A + B) = \sim A ? \sim B$                     |

| (a3) A ? $1 = A$            | (b3) A ? (B+C) = (A?B) + (A?C)                                                     |                                                           |

| (a4) $A + 1 = 1$            | (b4) A ? (B?C) = (A?B) ? C                                                         | d. Other Rules                                            |

| (a5) $A ? A = A$            | (b5) A + (B+C) = (A+B) + C                                                         | $(d1)A : B = \sim A?B + A? \sim B$                        |

| (a6) A + A = A              | (b6) A + (A?B) = A                                                                 | $(d1)A \operatorname{xor} B = \sim AandB +$               |

|                             |                                                                                    | Aand~B                                                    |

| (a7) A? $\sim$ A = 0        | (b7) A? $(A+B) = A$                                                                | $(d2) \sim (A!  B) = \sim A? \sim B + A?B$                |

| (a8) $A + \sim A = 1$       | (b8) A? $(~A + B) = A? B$                                                          | $(d2) \sim (A \operatorname{xor} B) = \sim Aand \sim B +$ |

|                             |                                                                                    | AandB                                                     |

| (a9) $\sim$ ( $\sim$ A) = A | $(b9) A + (\sim A ? B) = A + B$                                                    |                                                           |

|                             | $(b10) \sim \mathbf{A} + (\mathbf{A} ? \mathbf{B}) = \sim \mathbf{A} + \mathbf{B}$ |                                                           |

|                             | $(b11) \sim A + (A ? \sim B) = \sim A + \sim B$                                    |                                                           |

Note that the NOT operation is indicated here by ~ instead of as a bar over the letter. You are free to use either notation. You can indicate the rule by the letter. [Note to students: Unfortunately, the PDF writer has trouble with the symbol font. In the above chart, the ? in sections a, b and c are AND symbols and the meaning of the ? in section d can be found in the restatement of the rule.]

c. Using the Boolean Algebra rules shown above, prove that this combination of gates works as a NOR gate.

| $F = \sim [\sim (\sim A and \sim B)]$ | given   |

|---------------------------------------|---------|

| $F = \neg A and \neg B$               | rule a9 |

| $F = \sim (A \text{ or } B)$          | rule c2 |

This is a NOR gate.

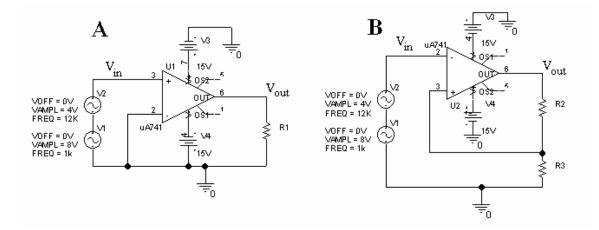

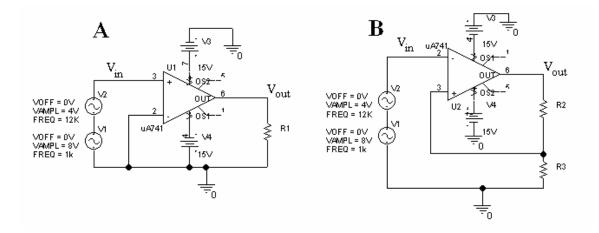

# Sample Question: Schmitt Trigger

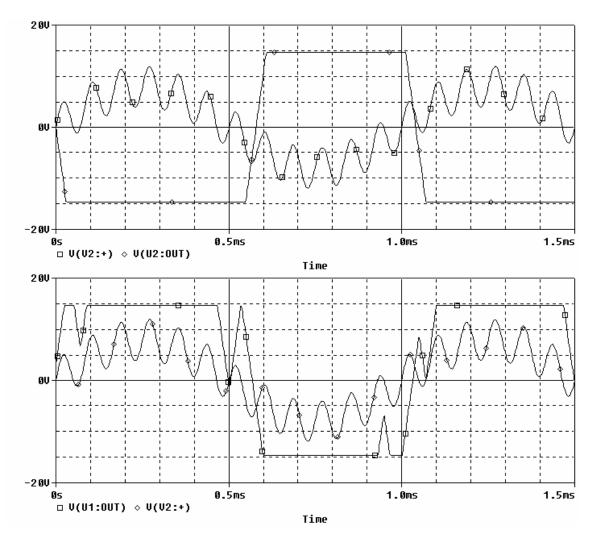

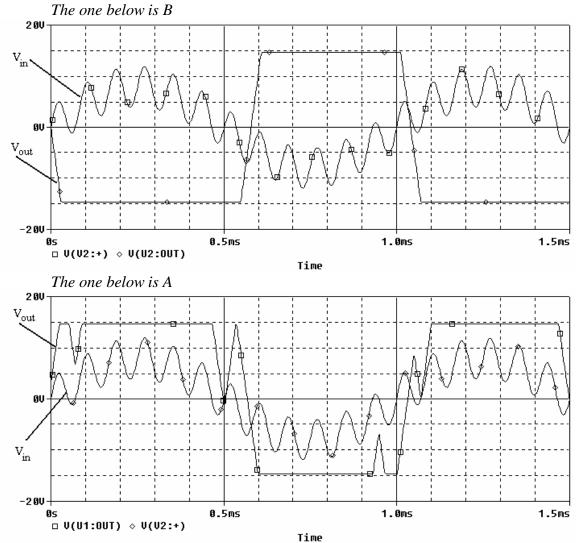

a) Indicate which plot below goes with which circuit above (2 pts) AND indicate Vin and Vout on both plots (4 pts).

- b) What is circuit A a model or example of ?

- a) an inverting amplifier b) a non-inverting amplifier

- c) a Schmitt trigger d) a comparator

- c) What is circuit B a model or example of ?

- a) an inverting amplifier b) a non-inverting amplifier

- c) a Schmitt trigger d) a comparator

- e) What is the saturation range of the op-amp (in both circuits)?

f) If R2 is 10K ohms, then what does R3 have to be in circuit B to give a hysteresis of 4 volts?

## 3) Schmitt Trigger (20 Points) \*\* ANSWER \*\*

a) Indicate which plot below goes with which circuit above AND indicate Vin and Vout on both plots .

b) What is circuit A a model or example of ?

| a) an inverting amplifier               | b) a non-inverting amplifier |

|-----------------------------------------|------------------------------|

| c) a Schmitt trigger                    | <u>d) a comparator</u>       |

| c) What is circuit B a model or example | of ?                         |

| a) an inverting amplifier               | b) a non-inverting amplifier |

| <u>c) a Schmitt trigger</u>             | d) a comparator              |

e) What is the saturation range of the op-amp (in both circuits)?

[From the plot, you can see that the op-amp saturates at between 14 and 15 volts when the positive is greater than the negative and between -14 and -15 volts when the negative is greater than the positive. Anything between (+15 to -15) and (+14 to -14) is acceptable. The value below is the actual value from PSpice for the above plots.]

Answer: +14.6 to -14.6 V

f) If R2 is 10K ohms, then what does R3 have to be in circuit B to give a hysteresis of 4 volts?

[Recalling your notes and section 6.5 in Lunn, the hysteresis is determined by the relationship between the saturation voltage and the two resistors in the voltage divider in circuit B. If we let Vref be the voltage point between R2 and R3, then Vref = Vout \* R3/(R2+R3). Since Vout toggles between +14.6V and -14.6V, we have two values for Vref:

+Vref = +14.6 \* R3 / (R2+R3) = +14.6 \* R3 / (R3 + 10K)-Vref = -14.6 \* R3 / (R2+R3) = -14.6 \* R3 / (R3 + 10K)

If we we want a range of 4 volts between +Vref and –Vref, then +Vref must be 2V and – Vref must be –2V. (The hysteresis is centered around 0 volts.) Therefore we have, ]

Answer:

2V = 14.6V \* R3 / (R3 + 10K) 2R3 + 20K = 14.6R3 12.6R3 = 20KR3 = 1587 ohms

[Please note that in the first plot (circuit B) above, the hysteresis is not the same. If you look at the point at which Vout BEGINS to rise and fall, you can see that the hysteresis is between about +3 and -3 for a hysteresis of 6V. In the second plot (circuit A), the change in direction happens at zero because there is no hysteresis for a comparator.]

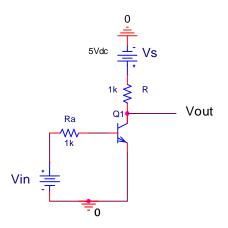

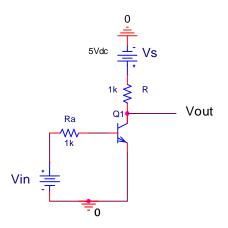

# **Sample Question: Transistors**

Here is a simple transistor circuit.

a) Redraw the circuit when Vin is 0V. [Draw the transistor as a switch either open or closed.]

b) Redraw the circuit when Vin is 5V. [Draw the transistor as a switch either open or closed.]

c) If Vin is the input, A, and Vout is the output, Y, then fill in the following truth table.

| A | Y |

|---|---|

| 0 |   |

| 1 |   |

d) What kind of gate is this?

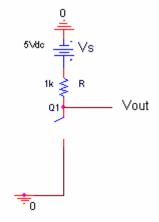

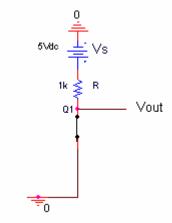

# Sample Question: Transistors \*\* ANSWERS \*\*

Here is a simple transistor circuit.

a) Redraw the circuit when Vin is 0V. [Draw the transistor as a switch either open or closed.]

b) Redraw the circuit when Vin is 5V. [Draw the transistor as a switch either open or closed.]

c) If Vin is the input, A, and Vout is the output, Y, then fill in the following truth table.

| A               | Y      |

|-----------------|--------|

| 0 ( <i>0V</i> ) | 1 (5V) |

| 1 (5V)          | 0 (0V) |

d) What kind of gate is this?

NOT gate